SEMICONDUCTOR

Kiểm soát tĩnh điện và bụi trong nhà máy sản xuất bán dẫn- Phần 1

Các vấn đề liên quan đến ESA/ESD trong sản xuất bán dẫn.

1. Bám hút tĩnh điện ( ESA)

1.1 Lực hút tĩnh điện gây hút các hạt bụi

Không giống như sản xuất điện tử và thiết bị bán dẫn đã đóng gói. Thách thức lớn nhất trong giai đoạn đầu sản xuất bán dẫn ( chế tạo Wafer) là bán hút tĩnh điện trong phòng sạch ( ESA). Điện trường do tĩnh điện gây ra khiến các hạt bụi di chuyển gây ô nhiễm bụi.

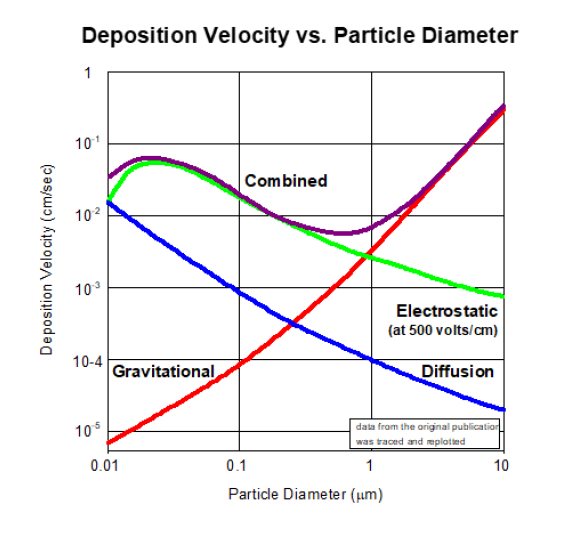

Tốc độ mà các hạt di chuyển trong không khí phụ thuộc vào điện trường và kích thước hạt bụi. Thông thường hạt bụi có kích thước lớn hơn 1mm ít bị ảnh hưởng bởi diện trường nhưng với kích thước nhỏ hơn <1mm thì nó lại ngược lại. Vận tốc lắng đọng là một thước đo để đánh giá ảnh hưởng của lực điện trường. Người ta tính ra rằng hạt bụi có kích thước 1mm bị hút về tấm wafer có điện trường 1000V/ inch (40kV/m) có lực hút gần bằng lực hấp dẫn tác động lên nó. Ngược lại hạt có kích thước 0.1mm có lực hút tĩnh điện gấp 100 lần lực hấp dẫn. Điều này cho thấy lực hút tĩnh điện khác nhau phụ thuộc vào kích thước và rất khó để đánh giá bằng mắt thường.

1.2 Điện trường tĩnh điện

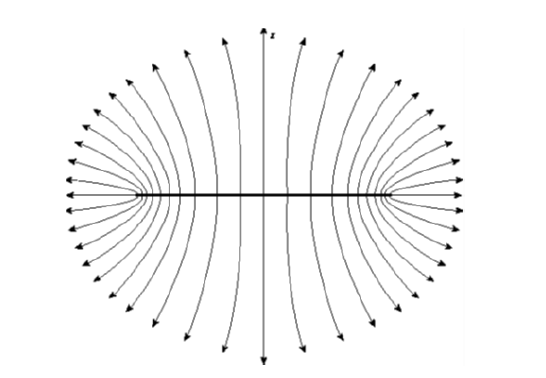

Điện trường sinh ra trên tấm wafer 300mm sẽ lớn hơn 300mm của tấm Wafer và nó không thể nhìn thấy bằng mắt thường. Một tấm wafer nhiễm tĩnh điện ở mức trung bình cũng có thể hút các hạt bụi ở gần tấm Wafer.

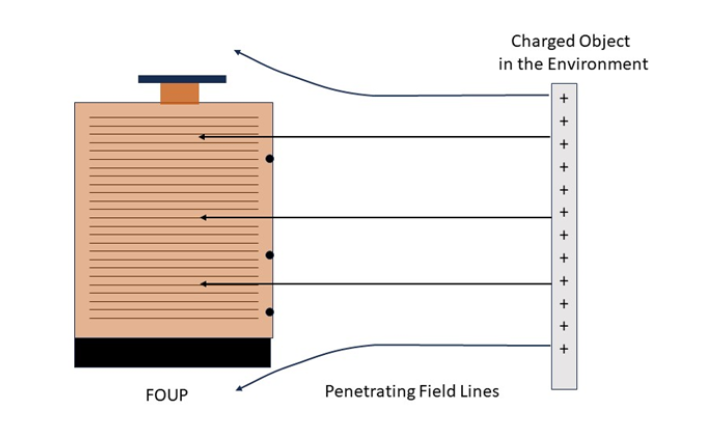

1.3 Xâm nhập của điện trường qua lớp vỏ cách điện

Điều quan trọng cần lưu ý là các đường điện trường có thể xuyên qua vật liệu cách điện. Điều này có nghĩa là một vật thể mang điện ở gần một vỏ nhựa, chẳng hạn như hộp giao diện cơ khí tiêu chuẩn (SMIF) hoặc hộp đựng wafer FOUP (Front Opening Unified Pod), có thể tạo ra các đường điện trường xuyên qua lớp vỏ. Các hạt bụi bám trên mặt trong của vỏ có thể bị bật ra do lực tĩnh điện và rơi xuống các tấm wafer. Vì lý do này, trong các nhà máy mini-environment, các tấm wafer và tấm quang khắc ( reticle) được lưu trữ trong hộp nhựa bảo vệ vẫn không an toàn trước các tác nhân ô nhiễm do các điện trường từ bên ngoài tác động lên hộp chứa. Điện tích trên các vật thể trong môi trường như cửa sổ, tường và rèm có thể là nguồn ô nhiễm tiềm ẩn và cần được loại bỏ .

1.4 Vật tích điện di chuyển và vật nối đất di chuyển

Một vật thể mang điện sẽ mang theo điện trường của nó khi di chuyển. Ví dụ, một xe đẩy hóa chất bằng nhựa di chuyển qua khu vực sản xuất trong nhà máy bán dẫn (fab). Khi xe đẩy đến gần một cassette wafer, các đường điện trường sẽ hướng về hoặc ra xa cassette. Sau khi xe đẩy đi qua, các đường điện trường đổi hướng ngược lại. Hệ quả là các hạt bụi bị đẩy qua lại do sự di chuyển trong fab và có thể dễ dàng bị tách ra, trôi nổi trong không khí và tìm đến một tấm wafer để gây ô nhiễm. Quá trình này giống như cách một máy khuấy hoạt động trong máy giặt.

Ngược lại, nếu vật thể đó là một vật dẫn được nối đất, các đường điện trường từ một vật thể mang điện gần đó sẽ kết thúc trên vật dẫn đó. Nếu vật dẫn này di chuyển, nó cũng sẽ có tác động đến sự ô nhiễm tương tự như một vật cách điện đang di chuyển.

1.5 Liên kết tĩnh điện

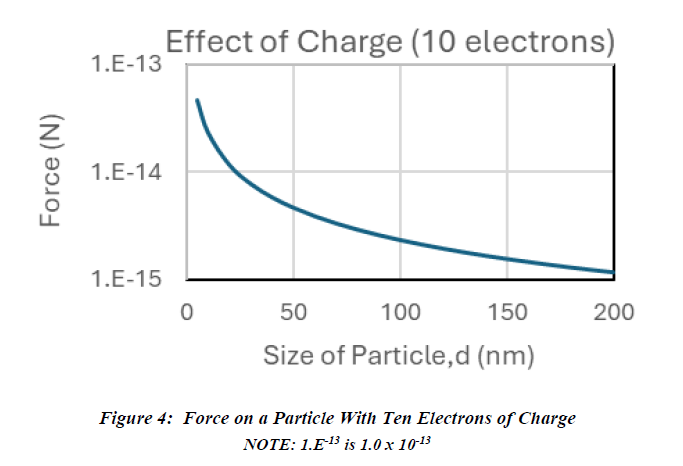

Các hạt mang điện tích vừa phải khi rơi xuống wafer có thể bị liên kết tĩnh điện với wafer. Hiệu ứng này càng mạnh đối với các hạt nhỏ hơn. Hạt nằm trên bề mặt wafer và cảm ứng ra một điện tích ảnh có độ lớn tương đương nhưng ngược dấu, vì wafer hoạt động như một tấm gương. Lực liên kết này được minh họa trong Hình 4 đối với các hạt có kích thước từ 1 nm đến 200 nm. Lực này lớn hơn lực hấp dẫn tác động lên hạt khoảng 8 đến 9 bậc! Điều đó có nghĩa là ngay cả những hạt mang điện tích tối thiểu cũng có thể không bị loại bỏ khỏi wafer bằng bất kỳ phương pháp làm sạch thông thường nào. Hiệu suất loại bỏ hạt thấp là một vấn đề đã được biết đến [4], và lực Coulomb này có thể giải thích hiện tượng đó.

1.7 Quy tắc kiểm soát ô nhiễm do lực tĩnh điện

Từ những phân tích trên, rõ ràng rằng việc kiểm soát lực tĩnh điện đóng vai trò quan trọng trong quản lý ô nhiễm. Điều này có nghĩa là các wafer trong quá trình xử lý phải được duy trì ở mức điện tích thấp. Theo tiêu chuẩn SEMI E78 [5], vào năm 2023, các wafer tiên tiến có kích thước nút hoặc kích thước đặc trưng (critical dimension – CD) 8,9 nm bị giới hạn ở mức trường tĩnh điện 8,9 V/cm trong khu vực xung quanh wafer (để tránh hư hỏng do tĩnh điện) và 0,12 nC (để kiểm soát ô nhiễm). Tương đương với 25V/inch

Mức điện tích cần được đo bằng Faraday Cup cỡ lớn có khả năng chứa wafer 300 mm, trong khi trường tĩnh điện nên được đo bằng các thiết bị phù hợp như đồng hồ đo điện áp tĩnh điện. Đây là các yêu cầu vô cùng nghiêm ngặt, khó đạt được nhưng vẫn có thể thực hiện được.

2. Kiểm soát ESD trong nhà máy sản xuất bán dẫn

So sánh các biện pháp kiểm soát ESD trong sản xuất được chứng nhận theo ANSI/ESD S20.20 hoặc IEC 61340-5-1 với thực tiễn tốt nhất trong kiểm soát ESD/ESA của ngành sản xuất bán dẫn

Mục tiêu của tiêu chuẩn ANSI/ESD S20.20 là đưa ra các yêu cầu cần thiết để thiết lập, thực hiện và duy trì chương trình kiểm soát phóng điện tĩnh điện (ESD) đối với các hoạt động sản xuất, xử lý, lắp ráp, lắp đặt, vận chuyển, đóng gói, dán nhãn, bảo trì, kiểm tra, thử nghiệm hoặc xử lý các bộ phận, cụm linh kiện và thiết bị điện tử dễ bị tổn thương do ESD.

Như đã đề cập trước đó trong tài liệu này, một số khác biệt chính giữa phạm vi áp dụng của ANSI/ESD S20.20 và chương trình kiểm soát ESD/ESA trong quy trình sản xuất bán dẫn ở giai đoạn đầu (FEOL – trước khi cắt hoặc đóng gói chip) là do khả năng và mức độ dễ dàng trong việc đưa năng lượng gây hư hỏng vào thiết bị.

- Các thiết bị đã hoàn thiện với dây nối, chân cắm và vỏ bọc có thể dễ dàng bị nhiễm năng lượng vào mạch bên trong, gây hư hỏng nghiêm trọng.

- Trong các xưởng sản xuất bán dẫn FEOL, tấm wafer chủ yếu bị ảnh hưởng bởi ô nhiễm do ESA, dẫn đến giảm hiệu suất sản xuất.

- Thực tiễn kiểm soát ESD/ESA trong sản xuất bán dẫn tập trung vào việc kiểm soát mức điện tích tĩnh điện trong các khu vực wafer di chuyển trong quá trình sản xuất.

Lý do chính cho các biện pháp kiểm soát này:

- Giảm ô nhiễm do điện tích tĩnh điện, giúp tăng hiệu suất sản xuất.

- Tránh sự cố ESD làm hỏng wafer, đảm bảo độ tin cậy của thiết bị.

- Ngăn chặn nhiễu điện từ (EMI) do sự kiện ESD, tránh gây gián đoạn hoạt động của hệ thống điều khiển máy móc trong xưởng sản xuất.

3.Ba nguyên tắc cơ bản của ANSI/ESD S20.20 có thể áp dụng cho kiểm soát ESD/ESA trong FEOL

- Nối đất hoặc liên kết tất cả các vật dẫn điện

- Trong sản xuất bán dẫn, điều này có nghĩa là các thiết bị và linh kiện liên quan phải được nối đất đúng cách và được kiểm tra định kỳ.

- Nếu thiết bị được di chuyển, cần có kế hoạch kiểm tra lại hệ thống nối đất trước khi tiếp tục xử lý wafer.

- Kiểm soát điện tích trên các vật cách điện cần thiết trong quy trình

- Cần ưu tiên sử dụng vật liệu chống tĩnh điện thay vì vật liệu cách điện và đảm bảo rằng chúng được nối đất đúng cách.

- Đối với các cửa sổ của máy móc, kiểm soát điện tích rất quan trọng để giảm nguy cơ ô nhiễm.

- Trong trường hợp các vật cách điện nằm trên đường di chuyển của wafer, cần triển khai hệ thống ion hóa để giảm mức điện tích xuống khoảng 100V.

- Ionizer cần được kiểm tra khi lắp đặt và có kế hoạch bảo trì định kỳ để đảm bảo hiệu quả hoạt động.

- Sử dụng bao bì bảo vệ khi vận chuyển và lưu trữ

- Wafer trong xưởng sản xuất thường được vận chuyển trong hộp chống tĩnh điện (đối với wafer ≤ 200mm) hoặc trong FOUPs (đối với wafer 300mm).

- FOUP có thể không cần phải là vật liệu chống tĩnh điện, nhưng thường có cấu trúc lược tiếp đất, giúp wafer luôn được nối đất trong quá trình di chuyển trên hệ thống vận chuyển tự động.

4. Xây dựng kế hoạch kiểm soát ESD/ESA trong xưởng sản xuất bán dẫn FEOL

- Một xưởng sản xuất bán dẫn FEOL có thể áp dụng ba nguyên tắc trên của ANSI/ESD S20.20 để xây dựng kế hoạch kiểm soát ESD/ESA.

- Kế hoạch này cần được điều chỉnh để đáp ứng các yêu cầu đặc thù, chẳng hạn như quy trình nối đất cho nhân viên khi xử lý wafer và reticle trong trường hợp khẩn cấp.

- Để đạt chứng nhận ANSI/ESD S20.20, cần nguồn lực đáng kể để xây dựng tài liệu kế hoạch, tổ chức đào tạo và triển khai chương trình kiểm tra tuân thủ.

- Ngay cả khi không cần đạt chứng nhận, việc có kế hoạch kiểm soát ESD/ESA có giám sát và đào tạo sẽ giúp giảm thiểu tổn thất sản xuất và đảm bảo độ tin cậy, đồng thời chứng minh với khách hàng rằng các biện pháp kiểm soát đang được thực hiện.

Việc quản lý kế hoạch kiểm soát ESD/ESA cần được thực hiện ở cấp độ quản lý đủ cao để có thể giám sát tất cả các bộ phận liên quan (quy trình, bảo trì, chất lượng, kiểm tra) nhằm đảm bảo mọi khía cạnh của kế hoạch đều được thực hiện đầy đủ.

4.1 Công đoạn EUV

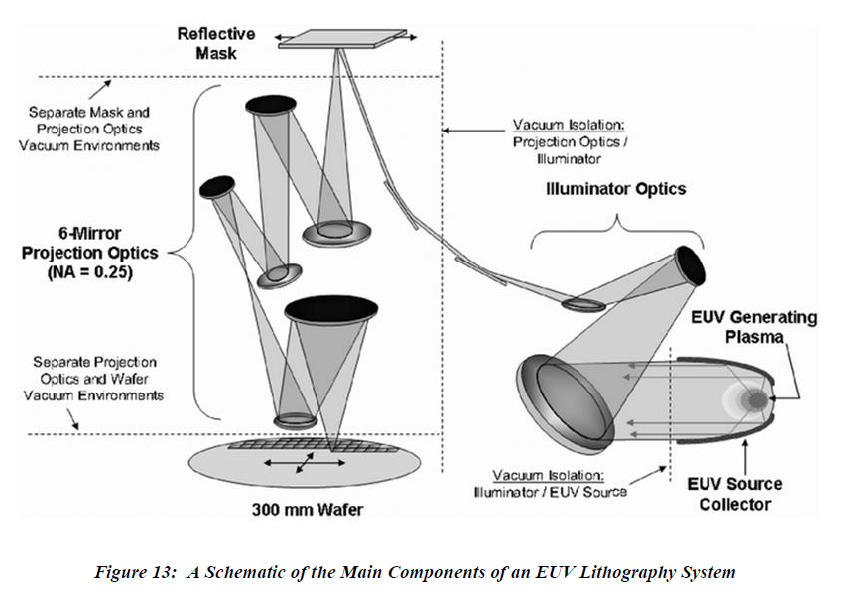

Công nghệ tiên tiến này đang nổi lên và chỉ được sử dụng bởi các nhà máy công nghệ cao nhất. Việc triển khai công nghệ hiện tại sử dụng các photon 13,5 nm để đạt được kích thước tính năng nhỏ của các mạch tích hợp rất hiện đại. Nó được thực hiện trong chân không vì cả không khí và nitơ đều không trong suốt đối với ánh sáng EUV. Nó sử dụng phản xạ từ bề mặt lưới vì thạch anh cũng không trong suốt đối với các photon 13,5 nm. Thay vì thấu kính, quang khắc EUV sử dụng gương không phẳng để tạo ra độ phóng đại âm để đạt được kích thước hình ảnh nhỏ chạm tới bề mặt wafer (xem Hình 13). Các lưới EUV có các lớp màng mỏng để kiểm soát ô nhiễm, giống như các lưới truyền dẫn.

4.2 Kết Nối Die-to-Die và Wafer-to-Wafer

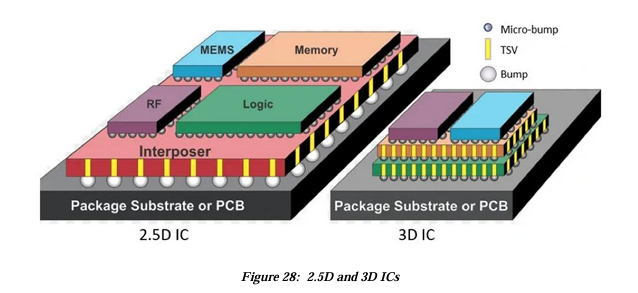

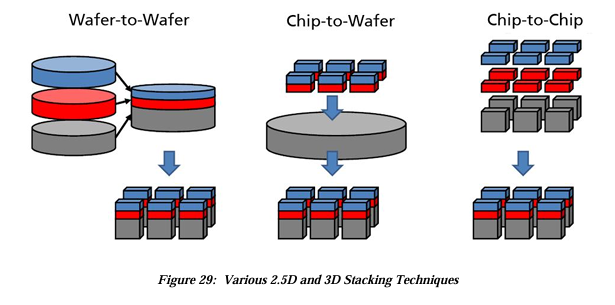

Heterogeneous Integration (tích hợp không đồng nhất), đặc biệt là công nghệ xếp chồng 2.5D và 3D, là một kỹ thuật lắp ráp bán dẫn (semi-fab) giúp kết nối trực tiếp các dies (hay còn gọi là chiplets) vào một gói mạch tích hợp duy nhất.

Lợi ích của công nghệ này:

- Mật độ linh kiện cao hơn

- Tăng hiệu suất hoạt động

- Giảm tiêu thụ điện năng do khoảng cách kết nối ngắn hơn

- Linh hoạt hơn trong thiết kế, vì chỉ những chiplets cần thiết mới được tích hợp vào gói mạch

So sánh công nghệ 2.5D và 3D stacking:

- 2.5D stacking:

- Các chiplets được đặt cạnh nhau trên interposer

- Interposer có mật độ kết nối cao hơn so với mạch in PCB truyền thống

- 3D stacking:

- Các chiplets được xếp chồng lên nhau theo chiều dọc

- Khoảng cách kết nối ngắn hơn so với 2.5D, giúp tiết kiệm không gian bề mặt ngang

Công nghệ hybrid bonding:

Ngành công nghiệp bán dẫn đã bắt đầu sử dụng hybrid bonding cùng với micro-bump bonding:

- Micro-bump: Kết nối các chiplets bằng hàn

- Hybrid bonding:

- Không cần hàn

- Liên kết dielectric giữa hai chiplets

- Kết nối điện thông qua tiếp xúc trực tiếp đồng-đồng (Cu-Cu)

Công nghệ hybrid bonding giúp giảm kích thước kết nối và cải thiện hiệu suất điện, phù hợp với xu hướng thu nhỏ và tối ưu hóa hiệu năng trong ngành bán dẫn.

Mức Mục Tiêu trong CDM ESD và Tác Động Đến Kết Nối Die-to-Die

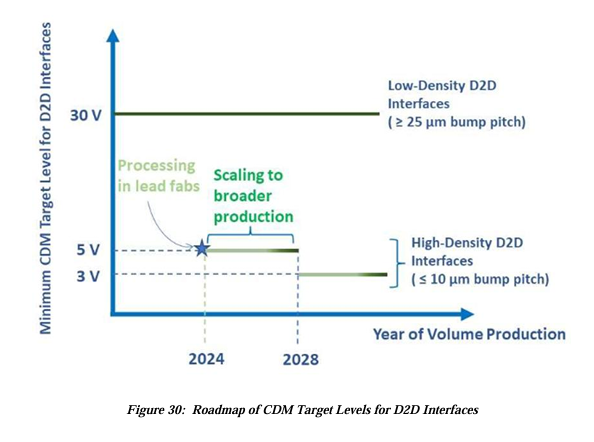

White Paper 2 của Target Levels đã công bố nghiên cứu về việc giảm tiêu chuẩn ESD CDM (Charged Device Model) ở cấp độ linh kiện, đặc biệt là trong giao diện Die-to-Die (D2D) của công nghệ xếp chồng 2.5D và 3D.

1. Sự khác biệt giữa kiểm tra CDM truyền thống và CDM trong quá trình 3D stacking

- Kết quả kiểm tra CDM trên IC truyền thống khác với CDM trên chiplet.

- Nguyên nhân chính: Điện trở của chân pogo trên máy thử CDM không tồn tại trong thực tế khi xảy ra xả tĩnh điện ở giao diện Die-to-Die, dẫn đến dòng điện đỉnh cao hơn ở cùng mức điện áp.

2. Các phương pháp đánh giá độ bền ESD của giao diện Die-to-Die

Hiện tại, có một số phương pháp thử nghiệm mới đang được phát triển để đánh giá độ bền ESD của giao diện D2D:

- VF-TLP (Very Fast Transmission Line Pulse)

- CC-TLP (Capacitively Coupled TLP)

- LICCDM (Low-Impedance Contact CDM)

- Phát hiện sự kiện điện từ (EM) bằng ăng-ten

3. Thách thức trong kiểm tra ESD ở mức độ chiplet

- Khi khoảng cách giữa các tiếp điểm điện của chiplet nhỏ hơn 10 μm, việc sử dụng TLP để đo lường trở nên gần như không khả thi.

- Một số công ty đã đóng gói chip/chiplet vào một gói thử nghiệm để thực hiện kiểm tra, nhưng điều này không phản ánh điều kiện thực tế, do gói thử nghiệm này không xuất hiện trong quá trình sử dụng thực tế của chiplet.

4. Xu hướng giảm mức tiêu chuẩn CDM trong tương lai

- Theo lộ trình của Industry Council, mức tiêu chuẩn CDM sẽ giảm xuống còn 5V vào năm 2024 và chỉ còn 3V vào năm 2028.

- Mức CDM thấp này đặt ra nhiều thách thức hơn đối với thiết kế và kiểm soát ESD trong quy trình sản xuất chiplet và 3D stacking.

4.4 Đo Đạc và Kiểm Soát Sự Kiện Xả Tĩnh Điện (ESD) Trong Giao Diện Die-to-Die

1. Đặc điểm của sự kiện phóng điện ở giao diện Die-to-Die

- Các phép đo sóng điện áp tại giao diện Die-to-Die đã cho thấy:

- Dòng điện đỉnh từ 100 mA đến hơn 1 A

- Thời gian tăng (rise time) từ 10 ps đến hơn 100 ps

- Mức độ phóng điện phụ thuộc vào:

- Điện dung nguồn ban đầu

- Lượng điện tích có trên die

- Kích thước và thiết kế của die

2. Thiếu tiêu chuẩn cụ thể về biện pháp bảo vệ ESD trong sản xuất Die-to-Die

- Hiện không có tiêu chuẩn chung về biện pháp bảo vệ ESD cho giao diện Die-to-Die trong dây chuyền sản xuất.

- Việc tạo ra một tiêu chuẩn duy nhất là không khả thi, vì:

- Mỗi công đoạn sản xuất có quy trình và thiết bị khác nhau.

- Vật liệu hoặc quy trình có thể thay đổi, ảnh hưởng đến rủi ro ESD.

- Cách tiếp cận tốt nhất là đánh giá từng quy trình sản xuất một cách riêng lẻ, dựa trên hướng dẫn của ANSI/ESD SP17.1.

3. Lợi ích của thiết kế Die-to-Wafer (D2W) và Wafer-to-Wafer (W2W)

- Khi gắn nhiều die trên wafer hoặc gắn wafer với wafer, điện dung tổng thể tăng lên, giúp:

- Tạo hiệu ứng ghép điện dung (capacitive coupling) giữa die và wafer.

- Giảm điện áp tĩnh điện khi tiếp xúc trong quá trình lắp ráp.

- Một số nghiên cứu cho rằng vẫn có sự trao đổi điện tích, nhưng với tốc độ chậm hơn, nhờ vào cơ chế ghép điện dung này.

4. Sử dụng ionizer để kiểm soát điện tích trên die và wafer

- Ionizer là phương pháp chính để giảm điện tích trên die hoặc wafer trước khi lắp ráp.

- Do mức chịu đựng điện áp của die có thể thấp đến 5V, nên:

- Ionizer cần được giám sát liên tục.

- Nếu không bảo trì đúng cách, ionizer có thể làm tăng điện tích trên die/wafer vượt quá giới hạn chịu đựng.

- Giải pháp tối ưu:

- Sử dụng ionizer tự cân bằng (inherently balanced ionizers) như soft X-ray ionizer (photon-ionizer) hoặc alpha ionizer, đảm bảo điện tích luôn duy trì ở mức gần bằng 0.

5. Kết luận

Các quy tắc đã thảo luận ở trên rất quan trọng để góp thủ tránh các vấn đề hư hỏng mặt nạ (mặt kẻ ô). Điều này có nghĩa là việc kiểm soát tĩnh điện phải được thực hiện nghiêm ngặt tại khu vực lưu trữ mặt nạ (ống chứa lưới) và thiết bị phơi sáng (bước). Các biện pháp kiểm soát này cũng phải được áp dụng cho các công cụ kiểm tra mặt nạ tự động, kính hiển thị vi thủ công, công cụ sửa chữa bằng laser và công cụ thay thế viên.

Một chương trình kiểm soát bao gồm các kết quả điện tĩnh:

- Loại bỏ các thiết bị điện ở bất cứ nơi nào có thể.

- Sử dụng điện phân tích vật liệu khi có thể.

- Sử dụng ion hóa không phù hợp cho các vật liệu bắt buộc trong quy trình.

- Nối đất tất cả các dây điện gần khu vực di chuyển của mặt nạ.

- Tuy nhiên, khi xử lý mặt nạ, cần lưu ý các đặc điểm sau:

- Mặt nạ truyền xuyên (mặt truyền) được làm từ thạch anh (thạch anh) và chrome.

- Thạch anh là một cách bắt buộc trong quy trình.

- Cấu hình chrome trên mặt nạ được thiết lập về điện, vì vậy chúng không thể và không thể kết nối với trái đất.

- Vòng bảo vệ (vòng bảo vệ) nên nổi (nổi), nhưng cần sử dụng ion hóa không khí để giảm thiểu tích điện.

- Các mặt nạ đặc biệt nằm bên dưới lớp vỏ cũng được thiết lập về điện và không thể thu phóng điện bằng máy ion hóa.

- Ion hóa học không được trang bị trên bề mặt mặt nạ chỉ được thực hiện khi không có hạt.

- Không thể phóng điện cho không gian giữa hạt và mặt nạ bằng ion hóa không khí vì khu vực này được thiết lập.

Liên Hệ Ngay Để Nhận Tư Vấn

Chuyên gia có nhiều năm kinh nghiệm đào tạo và tư vấn ESD cho các công ty sản xuất điện tử, bán dẫn hàng đầu Việt Nam :SEI, Samsung Electronic Viet Nam, Canon, LG Electronic, Jabil, Fushan,Fujikura, Samsung SDIV, Brother, Seoul Semiconductor, Luxshare, WNC, Wistron, VNPT,Vinfast..……

Có chứng chỉ kiểm toán viên ESD và kỹ sư chống tĩnh điện được công nhận trực tiếp bởi hiệp hội chống tĩnh điện ESDA, là đơn vị chịu trách nhiệm cho bộ tiêu chuẩn ANSI/ESD S2020-2021

Công ty ZCT Việt Nam

📞 Số điện thoại: 0332953518

📧 Email: info@zct.vn

🌐 Website: www.zct.vn

Khóa đào tạo này không chỉ giúp nâng cao năng lực đánh giá nội bộ về ESD mà còn hỗ trợ doanh nghiệp đảm bảo tuân thủ tiêu chuẩn ANSI/ESD S2020, giảm thiểu rủi ro hư hại linh kiện điện tử do tĩnh điện. Đừng bỏ lỡ cơ hội trở thành chuyên gia đánh giá viên nội bộ về ESD – đăng ký ngay hôm nay!